| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 | 31 |

- 컨벌루션 연산

- pygraphviz 설치 오류

- linux c++ 컴파일

- Data HAzard

- CUDA

- Makefile compile

- Pyvrilog tutorial

- CLOCK GATING

- Pyverilog 실행

- pytest-pythonpath 설치 오류

- linux makefile 작성

- 남산업힐

- Design DNN Accelerator

- linux c 컴파일

- gcc 컴파일

- 클럭 게이팅

- CDC

- 딥러닝 가속기

- 이진수 곱셈 알고리즘

- DNN Accelerator

- pyverilog 설치 오류

- Pyverilog 설치

- DNN 가속기

- systolic array

- gpgpu-sim

- Pyverilog 튜토리얼

- 대구 반도체 설계기업 특화

- AMBA

- makefile

- 데이터 해저드

- Today

- Total

오늘은 맑음

Vivado HLS Tutorial(HLS 기초) 본문

Vivado HLS Tutorial에서 제공하는 lab1을 따라 해보겠습니다.

이 Tutorial은 Xilinx에서 제공하는 tutorial source를 다운받았다고 가정한 상태로 진행하겠습니다.

Sign In

www.xilinx.com

위의 xilinx 링크를 들어가 다운 받으시거나 tutorial pdf에 링크가 있습니다.

https://docs.xilinx.com/v/u/2014.2-English/ug871-vivado-high-level-synthesis-tutorial

Vivado Design Suite Tutorial: High-Level Synthesis - 2014.2 English

docs.xilinx.com

1. Vivado HLS를 켭니다.

2. Create Project를 선택하여 첫 프로젝트를 생성해줍니다.

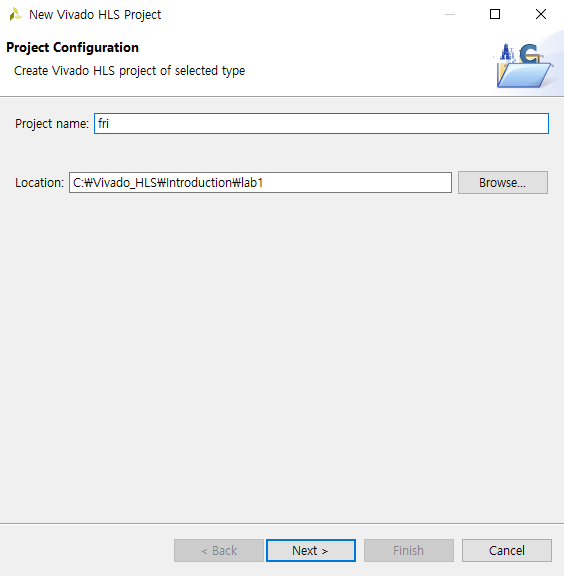

프로젝트 이름과 경로를 지정해줍니다.

project에서 사용할 source code를 넣어줍니다.

Top Function으로는 fir.c를 넣어주고 Next를 누른 후 TestBench에서 fir.test.c와 out.gold.dat파일을 넣어줍니다.

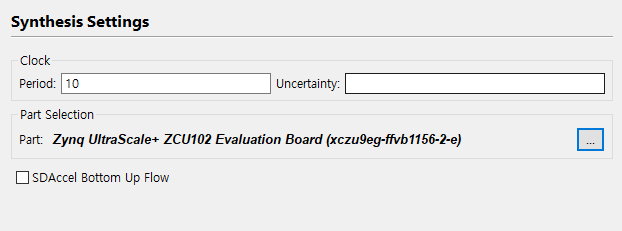

3. Synthesis Setting

tutorial대로 clock은 10ns로 세팅하였으나 저는 사용할 보드가 Zynq ultrascale+이라 따로 설정해주었습니다.

사용하시는 타겟 보드로 세팅하시면 되겠습니다.

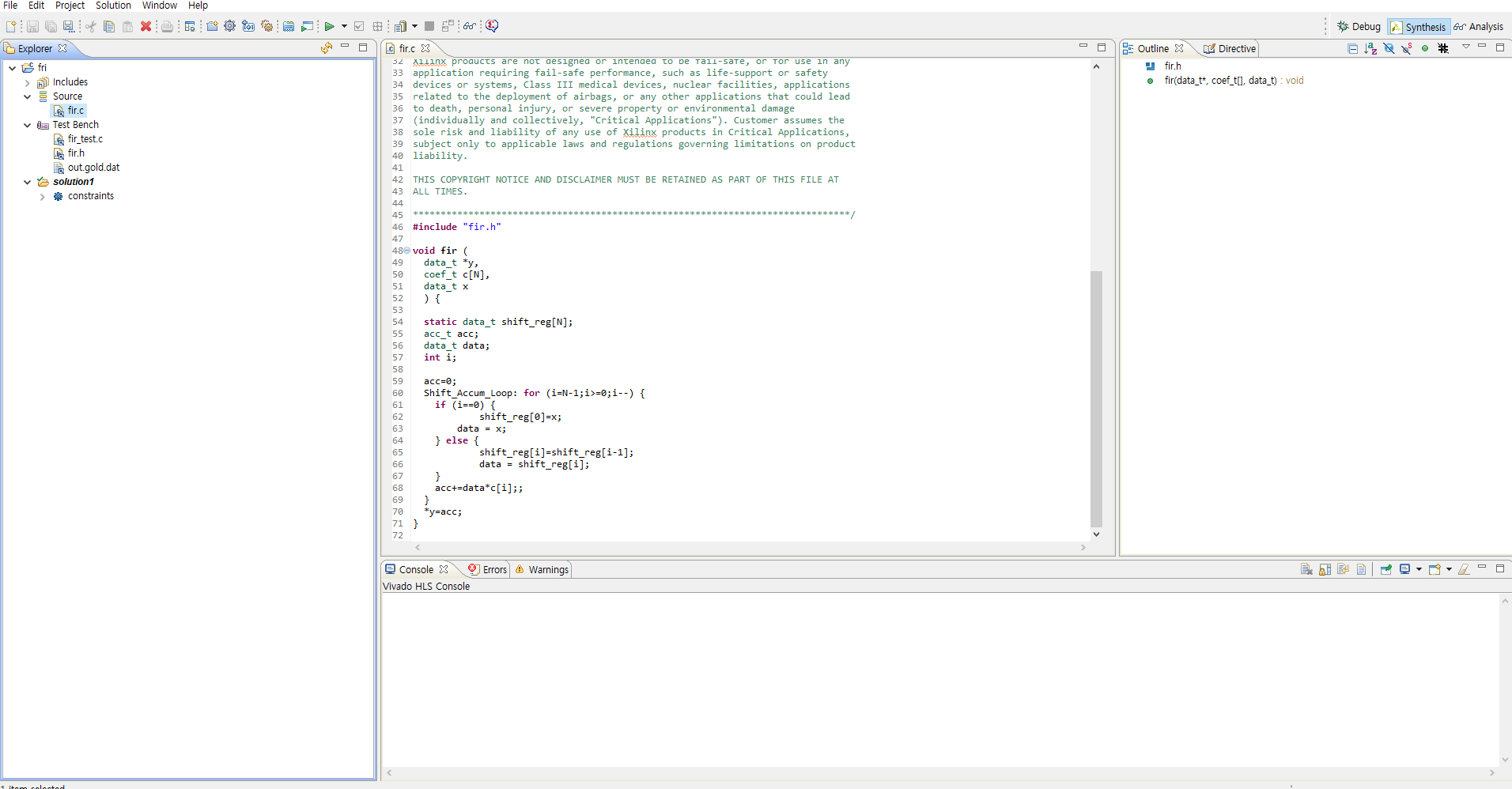

4. Project 화면

프로젝트 화면은 다음과 같습니다.

좌측에는 Project Explorer Pane이 있고 가운데는 source code 또는 각종 information이 나오는 Information Pane이 있으며 하단에는 Console Pane이 있습니다.

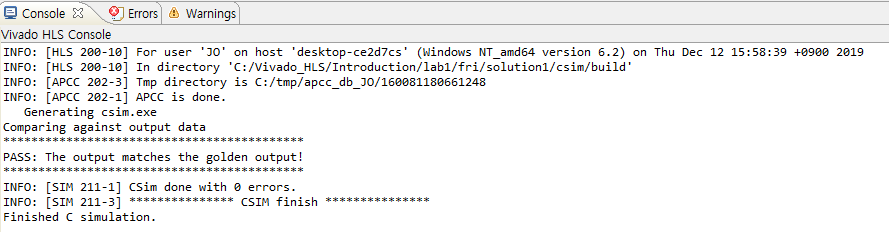

5. Run C Simulation

지금 Source에 올라와있는 fir.c를 fir_test.c를 이용하여 Simulation을 동작시킵니다.

Simulation의 코드에 따라 시뮬레이션이 올바르게 동작하였으면 PASS가 나옵니다.

정상적으로 Simulation이 동작한 것 같군요. Finished c simulation이라고 나옵니다.

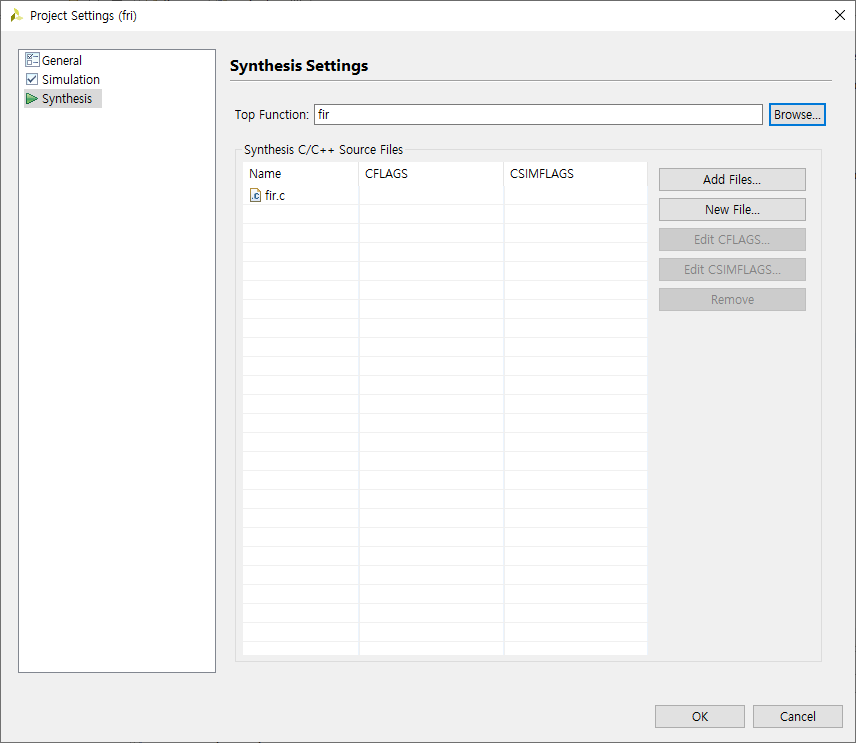

Simulation을 할 때 Top Function이 지정되지 않아 안 될 때가 있는데 Synthesis Settings에 들어가 Top Funtionc을 설정해주시면 되겠습니다.

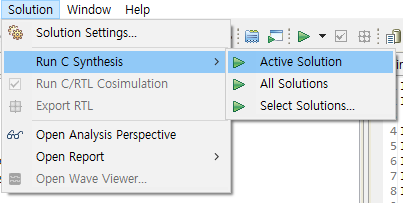

6. Run C Synthesis

이제 Simulation이 되었으니 source code에는 문제가 없이 동작하는 것이 확인되었습니다.

그러면 IP로 만들기 위해 합성을 해야겠죠?

그러기 위해 Solution -> Run C Synthesis-> Active Solution을 선택해 합성을 진행합니다.

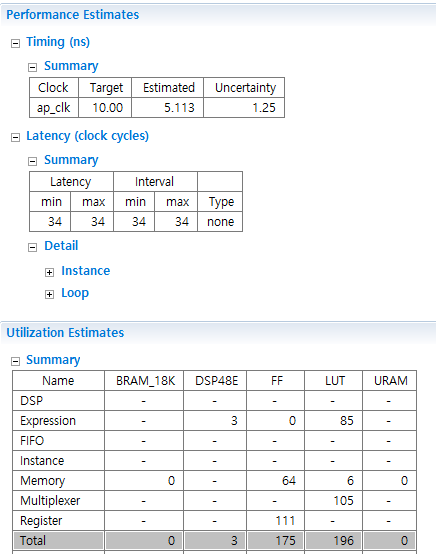

합성이 종료된 후에는 Information Pane에 합성 결과가 나옵니다.

Timing, Latency와 자원소모량등을 볼 수 있네요.

아래로 내리면 Interface도 볼 수 있습니다.

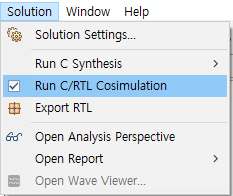

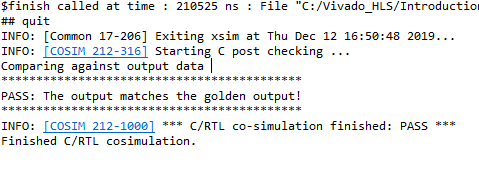

7. Run C/RTL Cosimulation

RTL simulation을 하기 위해 C test bench의 내용을 사용합니다.

Vivado simulator와 Verilog RTL을 사용하여 Cosimulation을 진행합니다.

이번에는 C simulation과는 다르게 C/RTL cosimulation이라고 나옵니다.

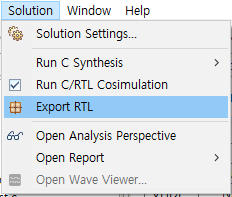

8. IP Creation

이제 C/RTL cosimulation을 통해 RTL에서도 simulation이 동작했음을 확인했습니다.

그러면 IP로 만들어서 사용해야겠죠?

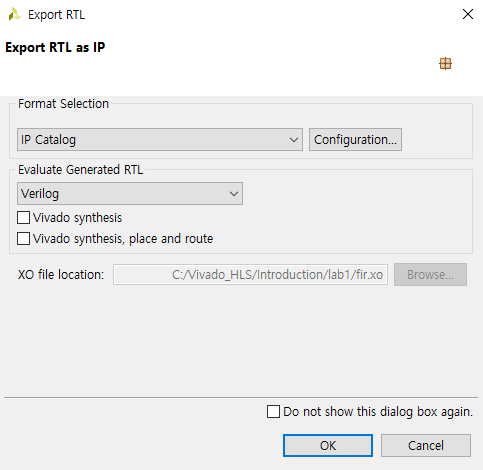

그러기 위해 Solution -> Export RTL을 눌러 RTL형태의 IP를 생성합니다.

IP를 만들어줄 때 format을 IP Catalog방식으로 생성해줍니다.

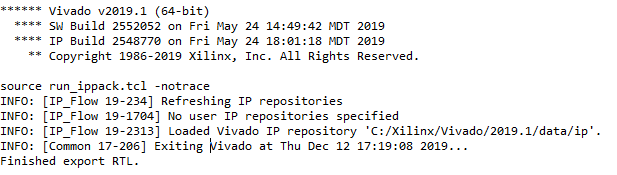

Export RTL

export RTL이 완료되면 다음과 같이 Finished export RTL이라는 문구가 뜹니다.

생성된 IP는 좌측의 Project Explorer Pane에서 solution -> impl -> ip를 보시면 xilinx_com_hls_fir_1_0.zip이라는 이름으로 확인할 수 있습니다.

'Tools > Vivado' 카테고리의 다른 글

| Vivado Tutorial / Vivado 시작하기 (0) | 2021.04.10 |

|---|---|

| Vivado Tutorial / Vivado WebPACK Edition 설치 (3) | 2021.04.10 |

| Vivado HLS(High Level Synthesis) (0) | 2019.12.12 |