| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |

- Pyvrilog tutorial

- CUDA

- linux makefile 작성

- pyverilog 설치 오류

- systolic array

- gcc 컴파일

- Pyverilog 실행

- Data HAzard

- 남산업힐

- pytest-pythonpath 설치 오류

- Makefile compile

- 컨벌루션 연산

- 딥러닝 가속기

- makefile

- AMBA

- 데이터 해저드

- CDC

- gpgpu-sim

- pygraphviz 설치 오류

- Pyverilog 설치

- Design DNN Accelerator

- linux c 컴파일

- Pyverilog 튜토리얼

- DNN 가속기

- 이진수 곱셈 알고리즘

- DNN Accelerator

- linux c++ 컴파일

- CLOCK GATING

- 대구 반도체 설계기업 특화

- 클럭 게이팅

- Today

- Total

오늘은 맑음

CDC(Clock Domain Crossing) 본문

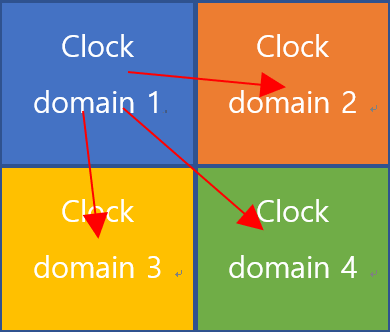

CDC라 함은 서로 다른 clock으로 동작하는 clock domain끼리 데이터를 전송하는 것을 의미합니다.

서로 다른 clock domain에 있는 Flip Flop끼리 데이터를 주고 받기 때문에 문제가 발생합니다.

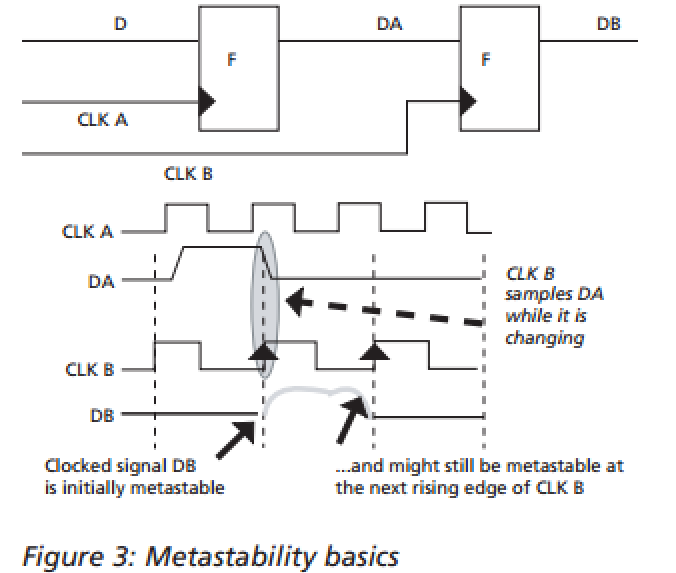

하나의 clock domain에서 데이터를 주고 받을 때 발생하지 않는 문제들이죠. 속도가 느린 Old Clock Domain과 속도가 빠른 New Clock Domain에서 데이터를 주고 받을 때를 가정하겠습니다. 만약 Old Clock Domain에서 데이터를 변경하는 동안 New Clock Domain의 clock이 rising edge가 되어 데이터를 받아간다면 이 때 가져간 데이터는 metastable state에 빠지게 됩니다. 충분히 안정되지 않은 데이터를 가져갔기 때문입니다.

Metastable state에 빠지게 되면 어떠한 값인지 알 수 없기 때문에 데이터를 받은 다른 clock domain은 제대로 된 동작을 할 수 없으며, 순간적으로 운이 좋게 동작하더라도 이후에는 동작이 되지 않을 수가 있습니다.

따라서 CDC에서 발생하는 문제를 해결하는 간단한 방법 몇가지를 알아보겠습니다.

1. Flip-Flop chain

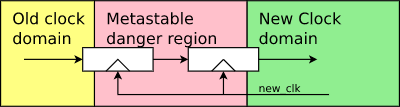

두 개의 clock domain 사이에 2개 혹은 3개 이상의 Flip-Flop chain을 사용(최신 공정에서는 4개까지 사용하는 경우도 있습니다. 몇개를 사용하는지는 정해진게 아니고, Old Clock Frequency, New Clock Frequency등 많은 요인에 의해 개수를 늘리기도, 줄이기도 합니다.)

New Clock Domain에 동기된 2개의 F/F chain을 이용하여 Old clock domain으로 부터 넘어오는 시그널을 받습니다. 첫 번째 F/F는 metastabe state가 될 확률이 높지만 두 번째 F/F는 metastable state가 될 확률이 낮기 때문에 데이터가 전달될 수 있습니다. 만약 여기서 두 번째 F/F의 출력 역시 meta data라면, F/F의 개수를 늘려야 하는 상황이 발생합니다.

이 방법은 Old clock domain이 New Clock domain보다 느린 동작주파수를 가질 때 유리합니다.

2. Asynchronous Reset Assertion, Synchronous Release

두 번째 방법은 비동기 reset을 사용한다. 비 동기 reset 신호와 함께 데이터를 전송시켜 Old clock domain과 New clock domain사이에 데이터를 동기적으로 전송하게 맞춥니다.

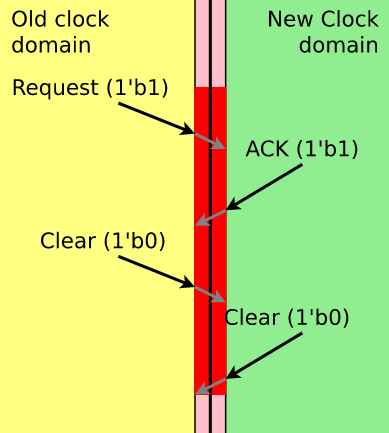

3. Handshake

1번과 2번의 방법에는 단점이 존재합니다.

New Clock domain에서 Old Clock domain으로부터의 출력이 수신되었는지를 확인할 수 없습니다.

예를 들어 느린 클럭에서 빠른 클럭으로, 빠른 클럭에서 느린 클럭으로, 또는 알려지지 않은 속도의 한 클럭에서 또 다른 클럭으로 데이터를 문제없이 이동시킬 수 있어야 한다. 이러한 단점을 보완하는 방법이 HandShaking signal을 사용하는 방법입니다.

위의 Request 신호부터 시간순서대로 주고 받습니다.

Old clock에서 전송된 Request 신호는 붉은색 영역인 metastability area를 통과하는데 이 때 F/F chain을 통과한다.

처음 Request signal이 전달될 때는 위에서 설명한 F/F chain과 같이 동작하지만 ACK신호가 돌아올 때는 Old Clock domain의 clock으로 동작을 합니다.

Request신호가 New Clock domain에 수신되면 request 신호는 clear됩니다.

역시 ACK신호가 Old Clock domain에 수신되면 New Clock domain의 ACK신호는 clear되며 ACK신호가 clear되기 전까지 어떠한 신호도 request되지 않습니다.

위의 방법이 CDC를 처리하는 모든 방법은 아닙니다. CDC상황에서 발생할 수 있는 문제는 매우 많고 해결하는 방법도 그만큼 많습니다. 앞으로 계속 공부하면서 차근차근 추가 정리 해보겠습니다.

https://wh00300.tistory.com/m/286

Multi-bit Synchronizer (CDC)

서로 다른 clock domain끼리 multi-bit의 데이터를 주고 받는 방법 중 gray code와 async fifo를 이용한 방법에 대해 알아보겠습니다. 이 전 글에서 알아본 것 처럼 2개 혹은 3개 이상의 fifo chain을 이용해서 CD

wh00300.tistory.com

출처 : https://zipcpu.com/blog/2017/10/20/cdc.html

Some Simple Clock-Domain Crossing Solutions

In many ways, metastability is the big boogeyman within FPGA design. It is hard to see when desk-checking a design, it doesn’t show up on all simulations (certainly not with Verilator), your synthesis tool can’t solve it, and timing analysis often just

zipcpu.com

'Digital logic' 카테고리의 다른 글

| Multiplication algorithm(2) (0) | 2020.04.17 |

|---|---|

| Multiplication algorithm(1) (0) | 2020.04.17 |

| Metastability/Metastable state (0) | 2019.12.04 |

| fpga와 asic설계시 유의사항 (0) | 2019.12.01 |

| module 사이의 데이터 전달 방법 (0) | 2019.11.30 |