| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |

- 컨벌루션 연산

- 클럭 게이팅

- 딥러닝 가속기

- linux makefile 작성

- makefile

- systolic array

- gpgpu-sim

- Data HAzard

- Pyverilog 튜토리얼

- CDC

- DNN Accelerator

- linux c 컴파일

- Pyverilog 설치

- pytest-pythonpath 설치 오류

- gcc 컴파일

- 이진수 곱셈 알고리즘

- linux c++ 컴파일

- 남산업힐

- Design DNN Accelerator

- pyverilog 설치 오류

- CUDA

- CLOCK GATING

- 데이터 해저드

- 대구 반도체 설계기업 특화

- AMBA

- DNN 가속기

- Makefile compile

- Pyvrilog tutorial

- Pyverilog 실행

- pygraphviz 설치 오류

- Today

- Total

오늘은 맑음

Combinational feedback loop란 본문

feedback loop는 나쁜 회로다.

조합 회로를 구성할 때 Combinational feedback loop가 없어야 한다.

라고 기술된 내용을 본 적이있을겁니다.

오늘은 combinational feedback loop에 대해서 알아보겠습니다.

먼저 Conbinational feedback loop는 회로에 치명적입니다.

feedback loop는 출력된 데이터가 다음 출력되는 데이터에 영향을 끼치는 구조를 의미합니다.

여기서 조심해야 하는 feedback loop란 출력이 안정되지 않는 loop를 의미합니다.

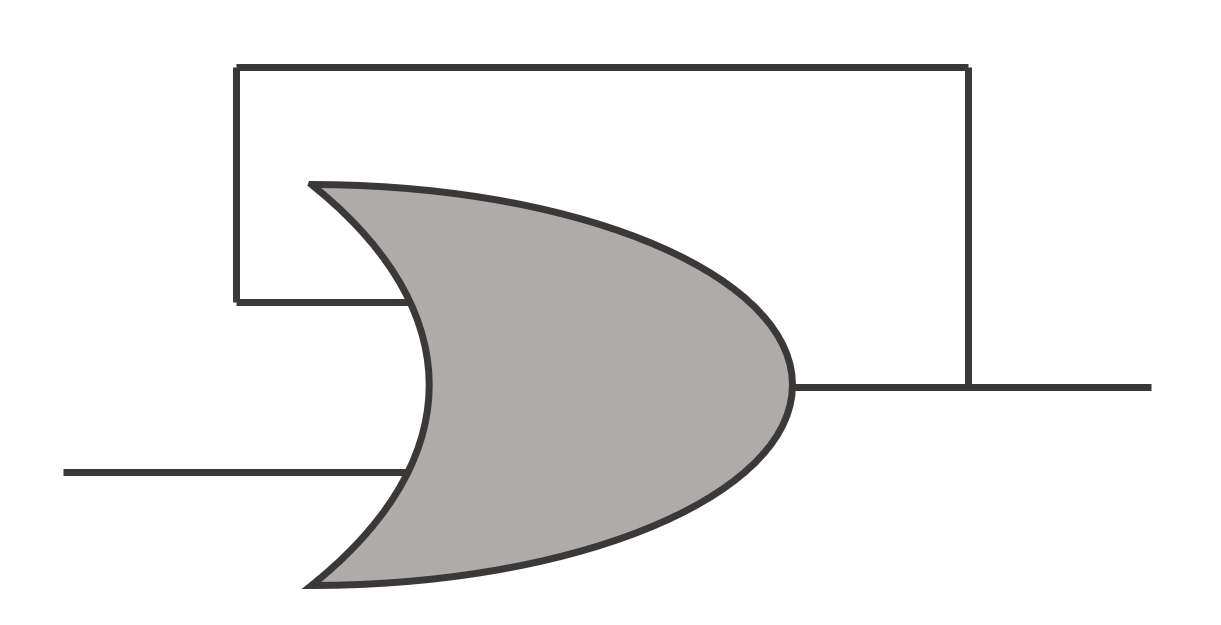

출력이 안정된 loop의 간단한 예시는 아래와 같습니다.

출력이 불안정한 loop의 간단한 예시는 or gate 대신 exclusive or gate가 위치하는 loop입니다.

exclusive or gate가 feedback loop에 들어가게 되면 입력이 고정되어도 출력은 무한히 oscilliation(진동)하여 안정된 출력을 가질 수 없게 됩니다.

실험에서는 and, or, xor gate를 사용해서 각각의 결과를 확인해보겠습니다.

실험

inpuat a;

output b;

reg reg_b;

always @(*) begin

reg_b = reg_b (&, |, ^) a;

end

assign b = reg_b;

위의 코드를 통해 진행하겠습니다.

1. and

처음 reg_b가 unknown인 상태에서 a에 0이 입력되었습니다.

and gate는 입력 모두 1이어야 1을 출력하게 되므로 출력이 0이 되어 안정된 출력을 내보내는 것을 볼 수 있습니다.

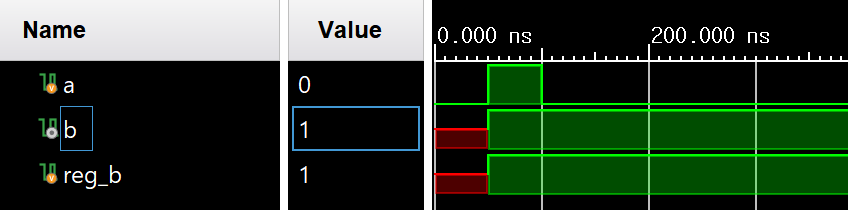

2. or

or gate를 사용했을 때는 처음 a가 입력되었을 때 b의 값이 unknown이므로 출력이 unknown이 됩니다.

하지만 a가 1이 되자 or gate의 출력은 1이 확실하게 되므로 출력값이 안정된 것을 볼 수 있습니다.

3. xor

xor gate는 a의 값이 어떤 값이 들어오더라도 출력값이 계속 진동해서 꾸준히 unknown값을 내보내는 것을 확인할 수 있습니다.

이러한 간단한 loop가 아니더라도 not gate를 사용하는 ring oscilliator 혹은 fsm 또는 두 개의 모듈 사이에서 데이터를 전달하는 과정에서도 combinational feedback loop가 발생할 수 있습니다. 결국 feedback loop로 인해 안정되지 않은 값이 출력되어 원하지 않는 출력을 얻게 되거나, hang이 발생해 시뮬레이션이 죽는 경우가 발생합니다. 따라서 Combinational feedback loop가 발생하지 않도록 항상 주의해야 합니다.

'Digital logic' 카테고리의 다른 글

| 디지털 회로 설계 과정(Front End) (4) | 2021.06.13 |

|---|---|

| active high와 active low (2) | 2021.05.16 |

| Clock Skew(클록 스큐) (0) | 2021.05.03 |

| verilog 문법(4) and/or 비트연산자, 논리연산자 (0) | 2021.05.01 |

| verilog 문법(3) part select (0) | 2021.04.24 |