| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |

- 이진수 곱셈 알고리즘

- linux c++ 컴파일

- 컨벌루션 연산

- DNN Accelerator

- AMBA

- Pyvrilog tutorial

- gpgpu-sim

- CLOCK GATING

- pyverilog 설치 오류

- 클럭 게이팅

- Pyverilog 실행

- Data HAzard

- 남산업힐

- CUDA

- CDC

- linux makefile 작성

- Pyverilog 튜토리얼

- systolic array

- 데이터 해저드

- gcc 컴파일

- pygraphviz 설치 오류

- makefile

- 대구 반도체 설계기업 특화

- 딥러닝 가속기

- linux c 컴파일

- Design DNN Accelerator

- Makefile compile

- pytest-pythonpath 설치 오류

- Pyverilog 설치

- DNN 가속기

- Today

- Total

오늘은 맑음

CDC: Multi-bit Synchronizer 본문

서로 다른 clock domain끼리 multi-bit의 데이터를 주고 받는 방법 중 gray code와 async fifo를 이용한 방법에 대해 알아보겠습니다.

이 전 글에서 알아본 것 처럼 2개 혹은 3개 이상의 fifo chain을 이용해서 CDC를 해결하는 할 수 있지만 이 방법은 multi-bit의 데이터를 주고 받기에는 적합하지 않습니다. 이유는 clock skew와 같은 이유로 모든 데이터가 동일한 타이밍에 switching되지 않을 수 있기 때문입니다.

아래 그림 1은 CLK domain의 128bit의 DATA가 CLK' domain으로 전달되는 모습입니다. 128bit의 데이터 중 1번 bit가 skew로 인해 CLK'의 posedge에 제대로 전달되지 않은 모습입니다. 이러한 상황에서 CLK' domain의 입장에서 10...1의 데이터가 정상적인 데이터인지 판단 할 수 없기 때문에 뒤로 에러가 전파됩니다.

Gray code를 사용하면 위와 같은 상황을 보완할 수 있습니다.

Gray code를 이용한 Gray counter는 한 번에 한 자리의 bit만 변화하기 때문에 데이터를 전송할 때 에러 검출을 위해 사용합니다.

10진수(0-15)를 2진수와 Gray code로 변경한 표 1을 보면 Binary는 3에서 4로 변할 때 0011에서 0100으로 총 세 자리의 bit가 변경 되었습니다. 하지만 Gray code는 0010에서 0110으로 세 번째 비트만 변경 된 것을 볼 수 있습니다.

이렇게 한 자리의 비트만 변경이 되기 때문에 Gray code를 사용했는데, 값이 바뀌었을 때 두 자리 이상의 비트가 변경 되면 데이터가 정상적으로 전달되지 않았다는 것을 알 수 있습니다.

그러면 어떻게 Gray code를 이용하여 multi-bit를 서로 다른 clock domain 사이에서 전달할 수 있는지 보겠습니다.

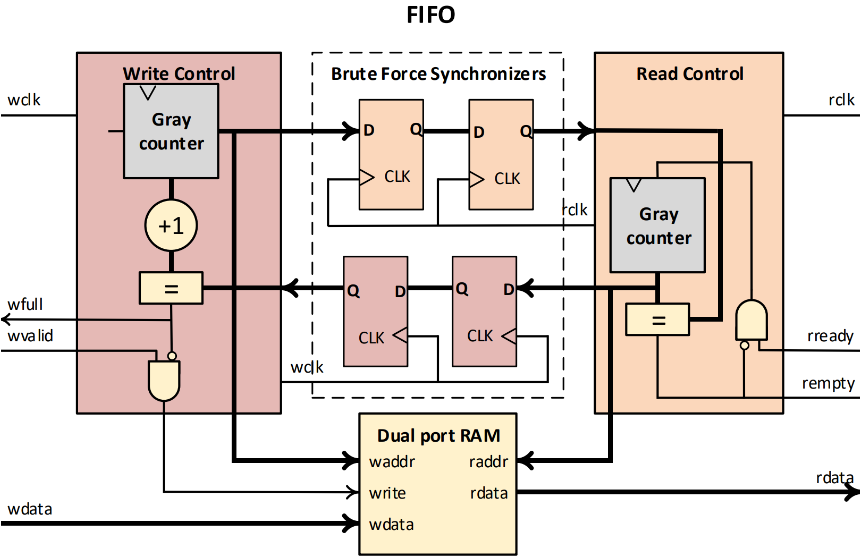

그림 2는 async fifo와 Gray counter를 이용한 multi-bit CDC 기법입니다. 각각 Gray counter를 포함한 Write Control, Read Contrl, Gray code를 전달하는 Brute Force Synchronizers와 Dual port RAM(혹은 async fifo)로 구성됩니다. 아래 글에서는 Dual port RAM을 fifo라고 표현하겠습니다.

Write Control

Wclk domain의 data를 fifo에 write할 때 사용하는 write address를 생성합니다.

Wvalid가 assert되면 Gray counter에서 생성된 waddr로 data가 write 됩니다.

Read Control로부터 raddr를 받아 fifo의 상태가 full인지 확인합니다.

Read Control

Write Control로부터 받은 write address를 받아 현재 raddr와 비교 후 fifo의 empty 상태를 체크합니다.

Rready가 assert 되면 Gray counter에서는 raddr를 생성하여 fifo로부터 데이터를 read합니다.

Brute Force Synchronizers

Write/Read Control에서 생성된 Gray code를 wclk domain과 rclk domain간에 전송해줍니다.

Dual port RAM/Async fifo

Wclk domain과 rclk domain에서 write/read할 수 있는 fifo입니다.

이 때 fifo의 데이터는 meta상태가 아니어야 합니다.

Gray code가 Brute Force Synchronizers를 통과하면서 fifo에 write된 데이터는 metastable(준안정) 상태에서 stable(안정) 상태로 변하게 됩니다.

수정사항

"gray code로 넘어온 read/write addr를 이용해서 error check를 한다"고 기재해 정정합니다. 만약 그렇게 되면 한 번의 write에 한 번의 read만 할 수 있어 error를 체크하지 않습니다.

만약 write보다 read의 동작 주파수가 낮아 write address를 놓쳐도 fifo의 동작에는 문제가 없습니다. Write에서 full check를 하기 때문에 overwrite는 발생하지 않기 때문입니다.

CDC(Clock Domain Crossing) (tistory.com)

CDC(Clock Domain Crossing)

CDC라 함은 서로 다른 clock으로 동작하는 clock domain끼리 데이터를 전송하는 것을 의미합니다. 서로 다른 clock domain에 있는 Flip Flop끼리 데이터를 주고 받기 때문에 문제가 발생합니다. 하나의 clock d

wh00300.tistory.com

Reference

PowerPoint Presentation (uio.no)

'Digital logic' 카테고리의 다른 글

| Digital logic에서 assert와 deassert란? (0) | 2023.08.07 |

|---|---|

| Timing analysis (2): RTL level에서 slack을 줄이는 방법 (2) | 2023.08.02 |

| Verilog HDL random, random 신호 생성하기 (2) | 2022.04.03 |

| CMOS 동작 원리와 장/단점 (0) | 2022.01.09 |

| 디지털 회로 설계 과정(Front End) (4) | 2021.06.13 |